数字集成电路CMOS电路检测

1对1客服专属服务,免费制定检测方案,15分钟极速响应

发布时间:2025-07-04 16:39:41 更新时间:2025-07-03 16:39:41

点击:0

作者:中科光析科学技术研究所检测中心

1对1客服专属服务,免费制定检测方案,15分钟极速响应

发布时间:2025-07-04 16:39:41 更新时间:2025-07-03 16:39:41

点击:0

作者:中科光析科学技术研究所检测中心

数字集成电路是现代电子系统的核心,其中CMOS(Complementary Metal-Oxide-Semiconductor)技术凭借其低功耗、高集成度和噪声抑制能力,在微处理器、存储器、通信芯片等领域占据主导地位。CMOS电路检测是确保集成电路可靠性、功能性和安全性的关键环节,涉及从设计验证到量产测试的全过程。随着半导体技术向纳米级发展,电路复杂度激增,检测需求愈发严格,以防止短路、开路、时序违规等潜在故障。检测不仅保证产品在极端环境下稳定运行,还降低返修成本和提高良率。在数字系统中,CMOS电路的检测重点关注逻辑功能、时序参数和电气特性,需结合模拟仿真和物理测试。全球半导体行业依赖于高效的检测流程,以应对5G、AI和物联网设备的高性能要求。本文详细探讨检测项目、仪器、方法及标准,为工程实践提供参考。

CMOS电路检测项目涵盖功能、性能、可靠性和环境适应性等多个维度。关键项目包括功能测试,验证逻辑门、寄存器及组合电路的正确执行;时序测试,检查时钟信号、设置/保持时间和传播延迟是否符合规范;功耗测试,测量静态功耗(漏电流)和动态功耗(开关能耗),优化能效比;噪声测试,评估电磁干扰(EMI)和热噪声对信号完整性的影响;故障覆盖率测试,通过故障注入模拟短路、断路等缺陷;可靠性测试,如加速寿命测试(HTOL)和电迁移分析,确保在高温、高压下长期稳定。此外,封装测试和ESD(静电放电)防护测试也是核心项目,保障芯片在现实环境中的耐用性。这些项目通过系统化矩阵覆盖设计、制造和应用的各个环节。

CMOS电路检测依赖先进的仪器设备,实现高精度、自动化操作。核心仪器包括自动测试设备(ATE),如Teradyne或Advantest系统,用于大规模生产测试,执行功能、时序和功耗分析;逻辑分析仪,捕捉和解析数字信号波形,识别逻辑错误;示波器(如Tektronix或Keysight型号),监测高速信号时序和抖动;扫描链测试器,通过JTAG接口访问内部节点,进行边界扫描;电源分析仪,精确测量静态和动态功耗参数;频谱分析仪,评估噪声和EMI干扰。此外,环境测试设备如恒温箱和振动台模拟极端条件,而故障分析工具(如电子显微镜和FIB系统)辅助物理缺陷定位。现代仪器集成AI算法,提升测试效率和覆盖率。

CMOS电路检测方法分为仿真测试和物理测试两大类。仿真方法包括功能仿真,使用EDA工具(如Cadence或Synopsys)模拟电路行为;时序仿真,分析信号传播路径;功耗仿真,预测能耗模型。物理方法涵盖静态测试,在稳态下检查逻辑输出;动态测试,施加激励信号模拟实际运行;边界扫描法(基于IEEE 1149.1标准),利用JTAG端口实现内部逻辑访问;内置自测试(BIST),在芯片内部嵌入测试逻辑,实现自我诊断;扫描测试法,将电路配置为扫描链,移位输入/输出数据;随机测试和算法测试,覆盖未知故障。高级方法如机器学习辅助测试,优化测试向量生成。这些方法确保高故障覆盖率(通常>95%)和低成本测试。

CMOS电路检测遵循国际和行业标准,确保测试一致性、互操作性和质量保证。核心标准包括IEEE 1149.1(JTAG标准),定义边界扫描架构;JEDEC JESD系列标准(如JESD22-A101 for 温度循环测试),规范可靠性测试条件;IEC 61000系列,规定电磁兼容性(EMC)测试要求;ISO 9001和IATF 16949,管理质量管理体系;IPC-A-610 for 封装和组装缺陷;MIL-STD-883 for 军工级可靠性。此外,行业特定标准如汽车电子AEC-Q100强调环境耐受性。测试报告需符合标准格式,如STDF(标准测试数据格式),促进数据交换。这些标准由IEEE、JEDEC和ISO组织维护,定期更新以适应技术演进。

证书编号:241520345370

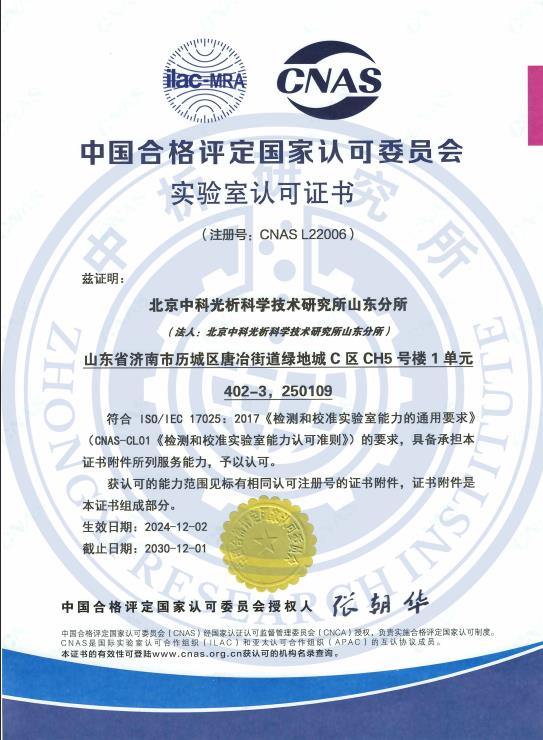

证书编号:CNAS L22006

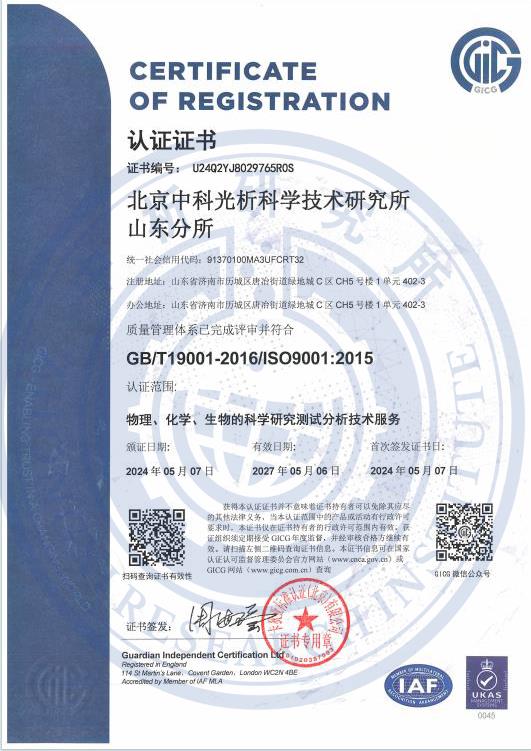

证书编号:ISO9001-2024001

版权所有:北京中科光析科学技术研究所京ICP备15067471号-33免责声明