输出允许时间和禁止时间(对三态输出)检测

1对1客服专属服务,免费制定检测方案,15分钟极速响应

发布时间:2025-04-24 23:32:16 更新时间:2025-05-13 19:38:26

点击:0

作者:中科光析科学技术研究所检测中心

1对1客服专属服务,免费制定检测方案,15分钟极速响应

发布时间:2025-04-24 23:32:16 更新时间:2025-05-13 19:38:26

点击:0

作者:中科光析科学技术研究所检测中心

在数字电路设计中,三态输出(Tri-state Output)是一种关键功能模块,广泛应用于总线系统、微处理器接口和通信设备中。其核心特点是能够通过控制信号使输出端进入高阻态(Z状态),从而避免多设备冲突。允许时间(Enable Time,tEN)和禁止时间(Disable Time,tDIS)是衡量三态输出性能的重要参数,直接影响电路的时序准确性和信号完整性。允许时间指从控制信号有效到输出端脱离高阻态并稳定输出的时间;禁止时间则是控制信号无效后输出端返回高阻态所需的时长。检测这两个参数对于确保系统兼容性、避免总线竞争和优化时序设计至关重要。

针对三态输出的允许时间和禁止时间检测,主要包含以下核心项目:

1. 允许时间(tEN):测量从控制信号(ENABLE)上升沿/下降沿到输出信号达到有效逻辑电平(高/低)的时间。

2. 禁止时间(tDIS):测量从控制信号(DISABLE)生效到输出端完全进入高阻态的时间。

3. 过渡过程特性:分析输出信号在切换过程中的上升/下降时间、过冲和振铃现象。

4. 负载依赖性测试:验证不同负载条件下tEN和tDIS的变化情况。

完成此类检测需依赖专业仪器设备,主要包括:

- 数字存储示波器(DSO):用于捕捉高精度时序波形,推荐带宽≥1GHz以捕获快速跳变沿。

- 逻辑分析仪:多通道同步采集控制信号与输出信号,便于时序对齐分析。

- 信号发生器:提供精准的控制信号(如ENABLE/DISABLE脉冲),需支持可调边沿速率。

- 三态缓冲器测试夹具:集成负载网络,模拟实际应用中的容性/阻性负载条件。

检测流程通常遵循以下步骤:

1. 信号配置:设置信号发生器输出ENABLE/DISABLE信号,并定义其上升/下降时间与电平阈值。

2. 测试点选取:在待测器件(DUT)的控制端和输出端接入示波器探头,确保接地回路最短化。

3. 触发设置:以ENABLE信号的边沿作为触发源,同步捕获控制信号与输出信号的时序关系。

4. 数据采集与分析:通过示波器的光标测量功能或自动参数分析工具,计算tEN和tDIS的实际值,并记录波形中的异常现象。

三态输出允许时间和禁止时间的检测需依据行业或企业标准执行,常见标准包括:

- JESD78B(集成电路闩锁测试标准):规定三态器件在极端条件下的时序稳定性要求。

- IEC 60747-2(半导体器件通用规范):定义输出切换时间的测试条件与合格判据。

- MIL-STD-883(军用器件测试方法):涵盖高可靠性场景下的时序参数验证流程。

- 企业专用规范:针对特定应用场景(如汽车电子、高速接口)制定的更严苛测试标准。

通过上述检测项目、仪器与方法的系统化实施,可有效评估三态输出的时序性能,确保其在复杂系统中的可靠性与兼容性。

证书编号:241520345370

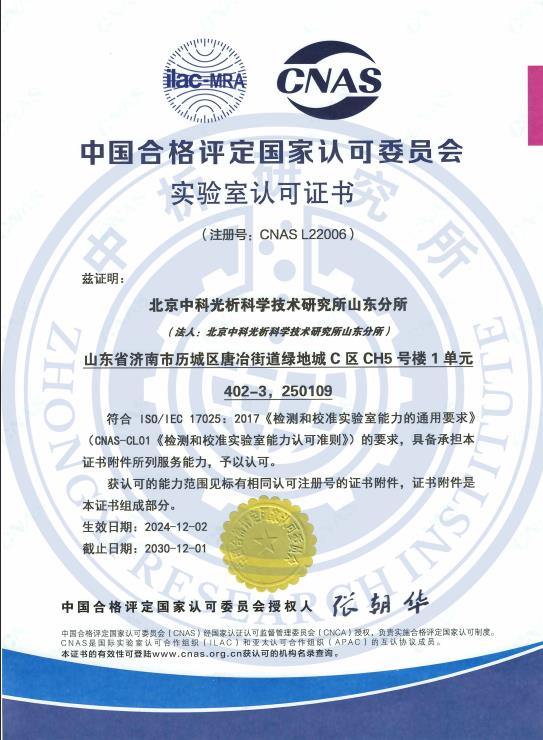

证书编号:CNAS L22006

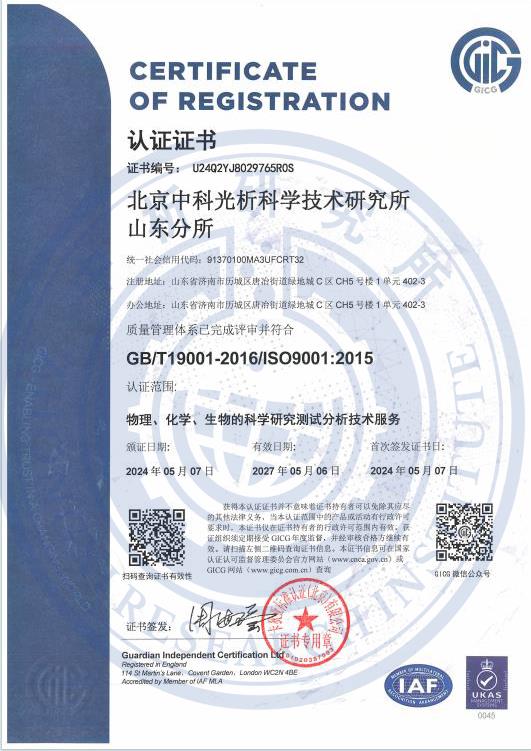

证书编号:ISO9001-2024001

版权所有:北京中科光析科学技术研究所京ICP备15067471号-33免责声明