建立时间和保持时间检测

1对1客服专属服务,免费制定检测方案,15分钟极速响应

发布时间:2025-04-24 23:34:26 更新时间:2025-05-27 21:19:25

点击:0

作者:中科光析科学技术研究所检测中心

1对1客服专属服务,免费制定检测方案,15分钟极速响应

发布时间:2025-04-24 23:34:26 更新时间:2025-05-27 21:19:25

点击:0

作者:中科光析科学技术研究所检测中心

建立时间(Setup Time)和保持时间(Hold Time)是数字电路设计中时序分析的核心参数,尤其在同步系统中对信号稳定性起决定性作用。建立时间指数据信号在时钟有效边沿到来前必须保持稳定的最短时间,而保持时间则是时钟边沿到达后数据信号仍需维持稳定的最短时间。二者共同确保触发器能够正确捕获数据。在高速电路、FPGA设计及芯片验证中,建立时间和保持时间的检测是验证时序约束、避免亚稳态问题的关键步骤。

建立时间和保持时间检测的主要项目包括:

1. 建立时间参数范围测试:验证数据信号在时钟边沿前的稳定性是否符合设计规格

2. 保持时间参数范围测试:评估时钟边沿后数据信号的稳定维持能力

3. 时序余量(Timing Margin)分析:确定系统在实际工作条件下的安全裕度

4. 温度/电压变化对时序的影响:在不同环境条件下测试时序参数的漂移情况

5. 信号完整性关联分析:包括信号抖动、噪声干扰对建立/保持时间的耦合效应

常用检测设备包括:

- 高速示波器(≥20GHz带宽):用于精确捕获时钟与数据信号的时序关系

- 时序分析仪:针对复杂时序系统提供自动化测量功能

- 逻辑分析仪:用于多通道信号同步分析与协议解码

- 信号发生器:生成可编程时钟和数据信号模式

- 环境试验箱:模拟温度、湿度等工况条件变化

标准检测流程分为以下步骤:

1. 信号同步校准:通过触发信号同步时钟与数据通道,消除探头延迟误差

2. 参数测量:使用眼图分析或余量测试法,量化建立/保持时间参数

3. 余量计算:通过改变时钟相位偏置,确定满足时序要求的安全窗口

4. 边界测试:在极限温度/电压条件下验证最坏情况时序余量

5. 统计分析:利用蒙特卡洛仿真评估工艺波动对时序的影响

主要遵循以下标准:

- JESD82-31:JEDEC发布的存储器接口时序测试规范

- IEC 62132:集成电路电磁兼容性测试中的时序相关要求

- 芯片厂商设计手册:如Xilinx UG903、Intel Timing Analyzer手册

- 行业协议标准:DDR、PCIe等接口协议中的时序参数定义

典型指标要求包括:建立时间余量≥10%时钟周期,保持时间余量≥50ps(根据工艺节点调整)

证书编号:241520345370

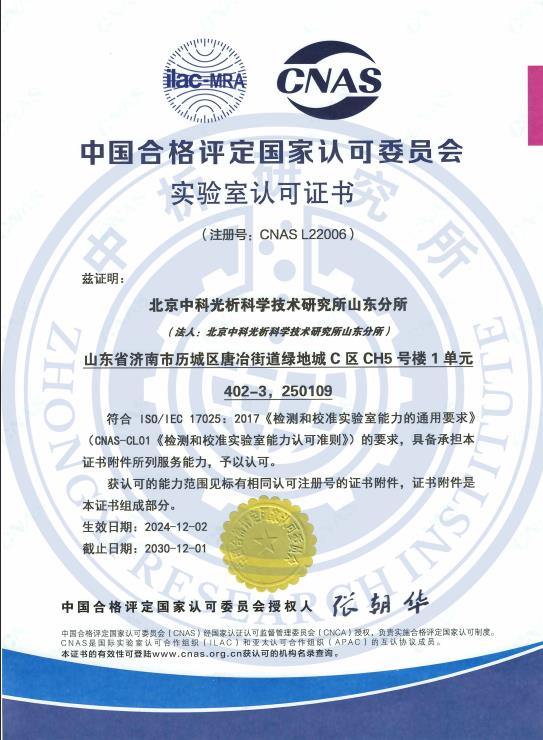

证书编号:CNAS L22006

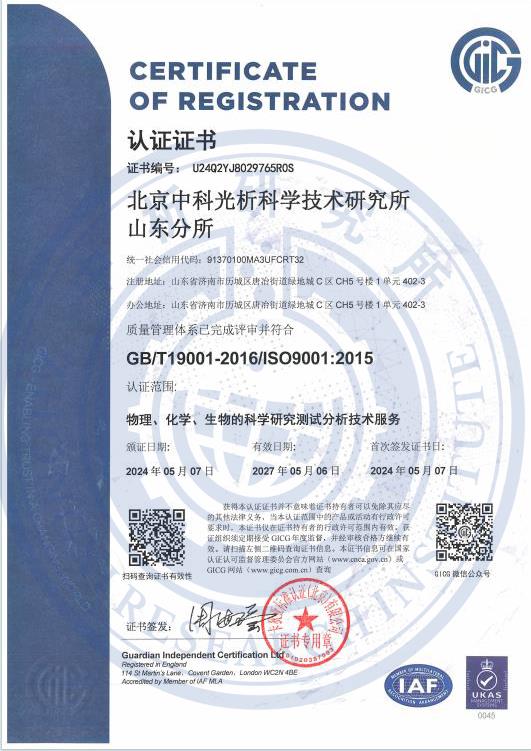

证书编号:ISO9001-2024001

版权所有:北京中科光析科学技术研究所京ICP备15067471号-33免责声明