晶片衬底检测:关键检测项目与技术解析

晶片衬底(Wafer Substrate)是半导体制造的核心基础材料,其质量直接决定芯片性能和良率。随着制程工艺向纳米级演进,衬底缺陷的检测要求愈发严苛。本文系统梳理晶片衬底检测的关键项目,涵盖物理、电学、化学等多维度检测技术。

一、晶片衬底检测的意义

晶片衬底是芯片制造的载体,需满足超高纯度、平整度及结构完整性要求。微小缺陷(如颗粒污染、晶体位错)可能导致后续光刻、刻蚀工艺失败。据统计,衬底质量问题占芯片总缺陷的15%-20%,检测环节可有效降低后续工艺风险。

二、核心检测项目分类

1. 物理特性检测

-

表面形貌检测

- 表面粗糙度(Roughness):原子力显微镜(AFM)测量纳米级起伏,标准值通常<0.2 nm RMS。

- 划痕与凹坑检测:激光散射仪识别微米级机械损伤,防止光刻胶涂布不均。

- 颗粒污染:光学表面扫描仪(如KLA-Tencor Surfscan)统计>30 nm颗粒密度,要求每平方厘米≤5颗粒。

-

几何参数检测

- 厚度均匀性:非接触式电容传感器检测300mm晶圆厚度波动需<1 μm。

- 翘曲度(Warp)与弯曲度(Bow):激光干涉仪测量晶圆平面度,翘曲度需<50 μm。

- 边缘轮廓:确保切割后边缘无崩缺,防止碎片污染。

2. 电学性能检测

- 电阻率(Resistivity):四探针法测量硅衬底电阻率(如P型硅0.1-100 Ω·cm)。

- 载流子寿命:微波光电导衰减法(μ-PCD)评估材料纯度,寿命>1 ms为合格。

- 介电强度:高压击穿测试氧化层质量,确保无局部漏电。

3. 化学成分与晶体结构检测

- 杂质浓度分析

- 二次离子质谱(SIMS):检测硼、磷等掺杂元素分布均匀性。

- X射线光电子能谱(XPS):分析表面金属污染(如Fe、Cu需<1e10 atoms/cm²)。

- 晶体缺陷检测

- X射线衍射(XRD):识别位错、层错等晶格畸变,摇摆曲线半高宽(FWHM)需<30 arcsec。

- 蚀刻坑检测:化学蚀刻后显微镜观察位错密度(要求<1e3/cm²)。

4. 表面洁净度检测

- 有机污染物:全反射红外光谱(ATR-FTIR)检测光阻残留。

- 金属离子污染:酸萃取-ICP-MS分析Na⁺、K⁺等含量(需<5e10 atoms/cm²)。

- 氧化物质量:椭偏仪测量氧化层厚度与均匀性(误差<±2%)。

三、先进检测技术应用

- 自动化光学检测(AOI): 高速高分辨率摄像头配合AI算法,实现亚微米缺陷实时分类(如区分划痕与颗粒)。

- 扫描电子显微镜(SEM): 用于纳米级缺陷的形貌与成分分析(如EDS能谱)。

- 太赫兹成像: 非接触式检测内部裂纹与空洞,穿透深度达数百微米。

四、检测数据管理与分析

- SPC(统计过程控制):实时监控关键参数(如厚度、电阻率)的CPK值,确保制程稳定。

- 缺陷分类与溯源:

- 分类:按类型(颗粒、划痕等)、位置、尺寸建立数据库。

- 溯源:结合检测数据与工艺参数,定位污染源(如研磨液杂质或设备磨损)。

五、行业趋势与挑战

- AI驱动的缺陷预测:利用机器学习模型关联检测数据与最终良率,提前预警潜在风险。

- 更高精度要求:3nm以下制程需检测0.5nm级表面起伏,推动AFM与电子束检测技术升级。

- 环保检测方案:开发无化学蚀刻的绿色检测工艺,减少废水排放。

六、结论

晶片衬底检测是半导体产业链的“守门员”,需多学科技术协同实现全维度质量管控。未来,随着检测精度与效率的持续提升,将推动半导体器件向更高集成度、更低功耗方向突破。企业需持续投入检测技术研发,构建涵盖“材料-工艺-设备”的闭环质控体系。

分享

CMA认证

检验检测机构资质认定证书

证书编号:241520345370

有效期至:2030年4月15日

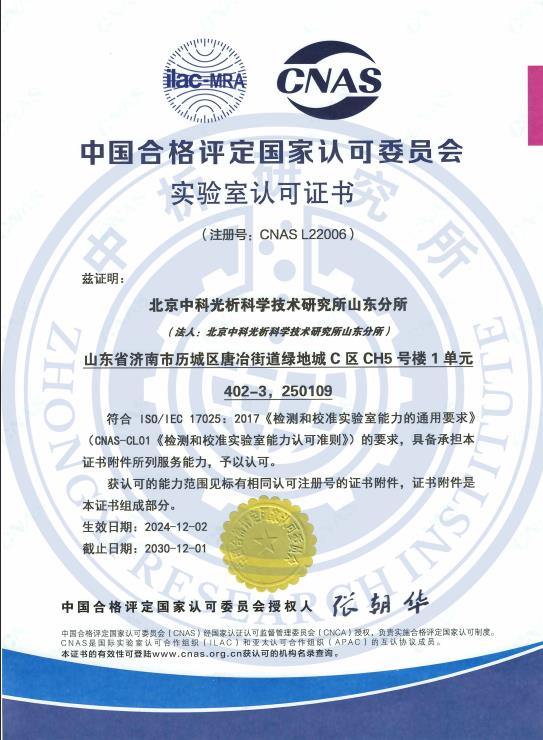

CNAS认可

实验室认可证书

证书编号:CNAS L22006

有效期至:2030年12月1日

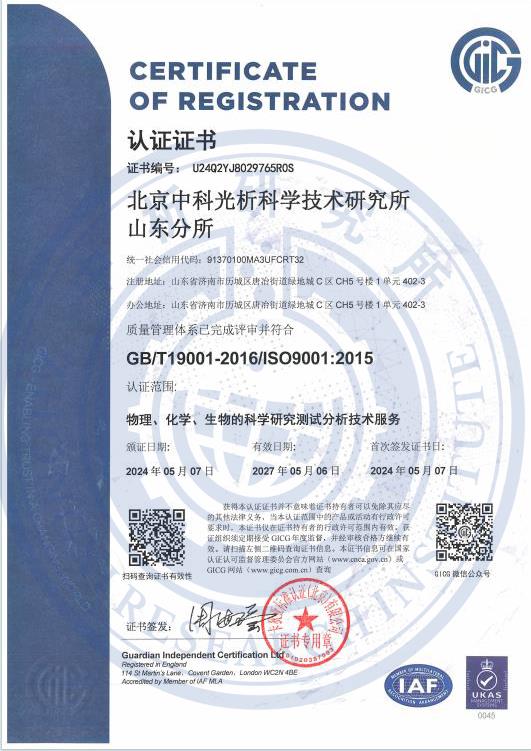

ISO认证

质量管理体系认证证书

证书编号:ISO9001-2024001

有效期至:2027年12月31日