裸芯片测试

1对1客服专属服务,免费制定检测方案,15分钟极速响应

发布时间:2025-06-16 13:50:03 更新时间:2025-06-15 13:59:05

点击:0

作者:中科光析科学技术研究所检测中心

1对1客服专属服务,免费制定检测方案,15分钟极速响应

发布时间:2025-06-16 13:50:03 更新时间:2025-06-15 13:59:05

点击:0

作者:中科光析科学技术研究所检测中心

裸芯片测试(Bare Die Testing)是指在集成电路封装前,对切割分离后的单个裸芯片进行的电气性能和功能验证。这是半导体制造流程中至关重要的质量控制环节,直接剔除有缺陷的芯片,避免不良品进入后续昂贵的封装阶段,有效降低成本并确保最终产品的良率和可靠性。裸芯片测试的重点检测项目涵盖多个层面:

DC参数测试:

IDD, ICC),识别短路、漏电或功耗异常。IIL, IIH): 测量输入引脚在施加低电平(VIL)或高电平(VIH)电压时的漏电流大小,判断输入缓冲器性能。VOL, VOH, IOL, IOH): 测量输出引脚在驱动规定负载电流 (IOL, IOH) 时的输出电压 (VOL, VOH),确保其能正确驱动负载。IOZL, IOZH): 测量输出引脚处于高阻态 (Z) 时的漏电流。VREF、内部电源轨)的电压值是否在允许范围内。RON): 对于功率器件或模拟开关,测量其导通状态下的电阻值。AC参数测试:

TPD, TPHL, TPLH): 测量信号从输入引脚变化到引起输出引脚响应所需的时间(包括上升和下降延迟)。TSU) 和保持时间 (TH): 验证时钟信号与数据信号之间的时序关系,确保数据在时钟有效边沿被正确捕获(尤其对存储单元、寄存器)。FMAX): 确定芯片在满足所有时序约束下能稳定工作的最高时钟频率。TR)、下降时间(TF): 验证时钟信号或控制信号的波形质量是否符合要求。TACC): 对于存储器类芯片,测量从地址有效到数据输出稳定所需的时间。功能测试:

IDDQ /静态电流测试:

IDDQ)。异常高的IDDQ通常指示存在制造缺陷,如栅氧短路、桥接短路等物理缺陷。扫描测试:

存储器内建自测试:

逻辑内建自测试:

边界扫描测试:

虽然一些严格意义上的寿命可靠性测试(如高温工作寿命测试 HTOL)通常在封装后进行,但裸芯片阶段可施加一些应力进行初步筛选:

VDD+) 和/或温度 (Tj+) 条件下,对芯片施加短暂的功能或向量测试 (Burn-in)。目的是加速潜在早期失效(如栅氧缺陷)的暴露,剔除“婴儿死亡率”高的芯片。此类测试常与电测结合或在其前后进行:

Gain)、噪声系数 (NF)、线性度 (IP3, P1dB)、输入/输出回波损耗 (S11, S22)、隔离度 (S12, S21)、相位噪声、杂散发射等。通常在特定频点下使用矢量网络分析仪等设备进行。Offset)、增益误差 (Gain Error)、非线性度 (INL, DNL - 尤其对ADC/DAC)。SNR)、总谐波失真 (THD)、无杂散动态范围 (SFDR)、建立时间 (Settling Time)。PSRR)、共模抑制比 (CMRR)。BV)、导通电阻 (RDS(on))、开关时间 (Ton, Toff)、阈值电压 (Vth)、栅极电荷 (Qg)、体二极管特性 (Vf, Trr)。裸芯片测试是一个多维度、多层次的质量保障过程。其核心检测项目围绕电性能达标(DC/AC参数)、功能正确性(功能/扫描测试)、结构完整性(DFT结构测试) 和潜在缺陷筛查(IDDQ/老化) 展开,辅以必要的物理外观与内部无损检查。对于特定类型的芯片(如RF、Analog、Power),还需进行专项的特殊性能参数测试。综合运用这些测试项目,才能有效地识别出制造缺陷、设计缺陷和早期可靠性问题,确保只有合格的裸芯片流入封装环节,为最终产品的性能和可靠性奠定坚实基础。测试策略的选择(如测试项目的组合、测试向量的覆盖度、测试条件的严苛度)需要根据芯片的复杂度、应用场景、成本目标以及良率要求进行精心设计和优化。

证书编号:241520345370

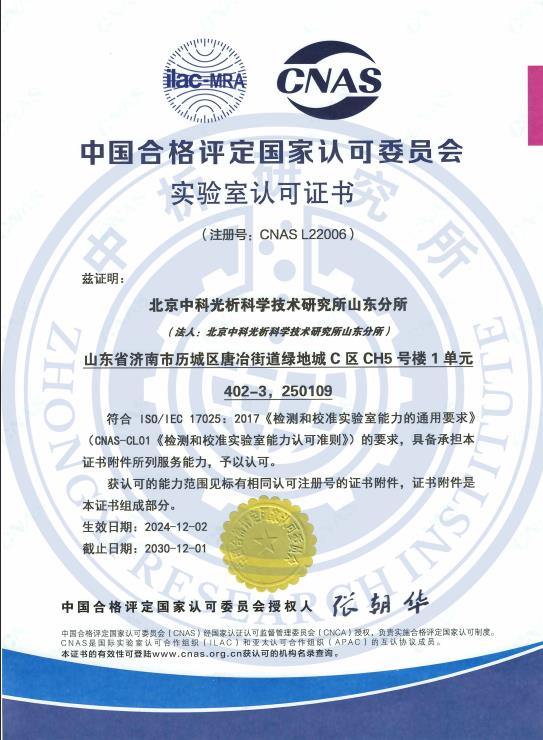

证书编号:CNAS L22006

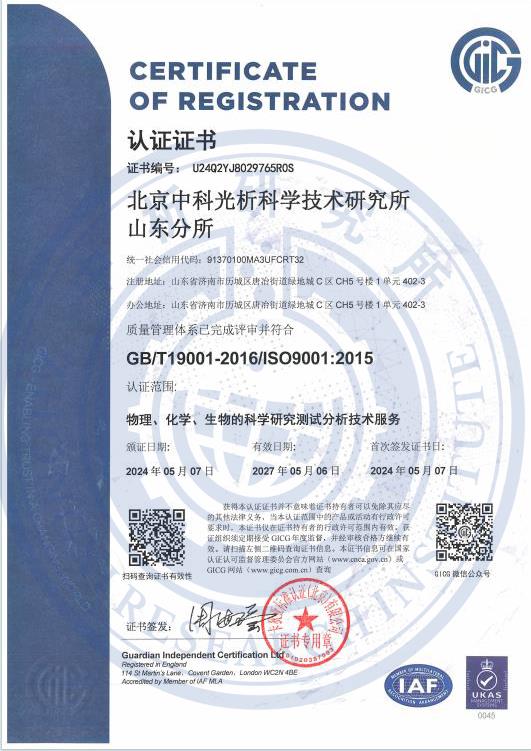

证书编号:ISO9001-2024001

版权所有:北京中科光析科学技术研究所京ICP备15067471号-33免责声明